Surat:info@anke-pcb.com

WhatApp/WeChat: 008618589033832

Skype: Sannyduanbsp

Tiga aspek untuk mengamankan integritas dayaDesain PCB

Dalam desain elektronik modern, integritas daya adalah bagian yang sangat diperlukan dari desain PCB. Untuk memastikan operasi yang stabil dan kinerja perangkat elektronik, kita harus mempertimbangkan dan merancang secara komprehensif dari sumber daya ke penerima.

Melalui merancang dan mengoptimalkan modul daya dengan hati -hati, pesawat lapisan dalam, dan chip catu daya dapat benar -benar mencapai integritas daya. Artikel ini akan mempelajari tiga aspek utama ini untuk memberikan panduan dan strategi praktis bagi perancang PCB.

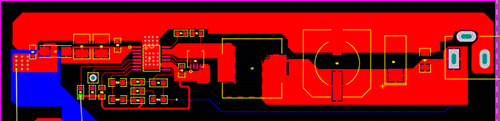

I. Kabel Tata Letak Modul Daya

Modul daya adalah sumber energi dari setiap perangkat elektronik, kinerja dan tata letaknya secara langsung mempengaruhi stabilitas dan efisiensi seluruh sistem. Tata letak dan perutean yang benar tidak hanya dapat mengurangi gangguan kebisingan tetapi juga memastikan aliran arus yang halus, sehingga meningkatkan kinerja keseluruhan.

2. Tata letak modul kekuatan

1. Pemrosesan Sumber:

Modul daya harus diberi perhatian khusus karena berfungsi sebagai titik awal daya. Untuk mengurangi pengenalan kebisingan, lingkungan di sekitar modul daya harus dijaga sebersih mungkin untuk menghindari kedekatan dengan yang lainfrekuensi tinggiatau komponen yang peka terhadap kebisingan.

2. Tutup ke chip catu daya:

Modul daya harus ditempatkan sedekat mungkin dengan chip yang disediakan daya. Ini dapat mengurangi kerugian dalam proses transmisi saat ini dan mengurangi persyaratan area bidang lapisan dalam.

3. Panaskan pertimbangan disipasi:

Modul daya dapat menghasilkan panas selama operasi, sehingga harus dipastikan bahwa tidak ada penghalang di atasnya untuk disipasi panas. Jika perlu, heatsink atau kipas dapat ditambahkan untuk pendinginan.

4. loop havoiding:

Saat routing, hindari membentuk loop arus untuk mengurangi kemungkinan gangguan elektromagnetik.

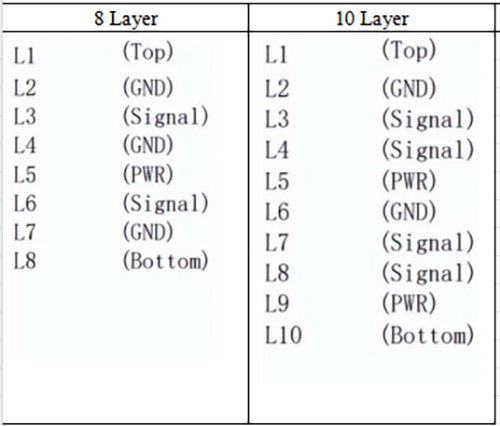

Ii. Perencanaan Desain Pesawat Lapisan Dalam

A. Desain Stack Lapisan

In Desain PCB EMC, Layer Stack Design adalah elemen kunci yang perlu mempertimbangkan perutean dan distribusi daya.

A. Untuk memastikan karakteristik impedansi yang rendah dari bidang listrik dan menyerap kopling noise tanah, jarak antara pesawat daya dan tanah tidak boleh melebihi 10mil, biasanya disarankan untuk kurang dari 5 juta.

B. Jika satu bidang daya tidak dapat diimplementasikan, lapisan permukaan dapat digunakan untuk meletakkan bidang daya. Bidang daya dan tanah yang berdekatan membentuk kapasitor pesawat dengan impedansi AC minimum dan karakteristik frekuensi tinggi yang sangat baik.

C. Hindari dua lapisan daya yang berdekatan, terutama dengan perbedaan tegangan yang besar, untuk mencegah kopling kebisingan. Jika tidak dapat dihindari, tingkatkan jarak antara dua lapisan daya sebanyak mungkin.

D. Bidang referensi, terutama bidang referensi daya, harus mempertahankan karakteristik impedansi rendah dan dapat dioptimalkan melalui kapasitor bypass dan penyesuaian lapisan.

B. Segmentasi kekuatan multiple

A. Untuk sumber daya rentang kecil tertentu, seperti tegangan kerja inti dari chip IC tertentu, tembaga harus diletakkan pada lapisan sinyal untuk memastikan integritas bidang daya, tetapi hindari meletakkan tembaga daya pada lapisan permukaan untuk mengurangi radiasi kebisingan.

B. Pemilihan lebar segmentasi harus sesuai. Ketika tegangan lebih besar dari 12V, lebar bisa 20-30 juta; Jika tidak, pilih 12-20mil. Lebar segmentasi antara sumber daya analog dan digital perlu ditingkatkan untuk mencegah daya digital mengganggu daya analog.

C. Jaringan daya sederhana harus diselesaikan pada lapisan perutean, dan jaringan daya yang lebih lama harus ditambahkan kapasitor filter.

D. Pesawat listrik yang tersegmentasi harus dijaga tetap teratur untuk menghindari bentuk yang tidak teratur yang menyebabkan resonansi dan peningkatan impedansi daya. Strip panjang dan sempit dan divisi berbentuk dumbel tidak diperbolehkan.

C. Penyaringan plan

A. Pesawat listrik harus dipasangkan erat dengan bidang tanah.

B. Untuk chip dengan frekuensi operasi yang melebihi 500MHz, terutama bergantung pada penyaringan kapasitor pesawat dan gunakan kombinasi penyaringan kapasitor. Efek penyaringan perlu dikonfirmasi oleh simulasi integritas daya.

C. Pasang induktor untuk kapasitor decoupling pada bidang kontrol, seperti pelebaran kapasitor dan meningkatkan vias kapasitor, untuk memastikan bahwa impedansi tanah lebih rendah daripada impedansi target.

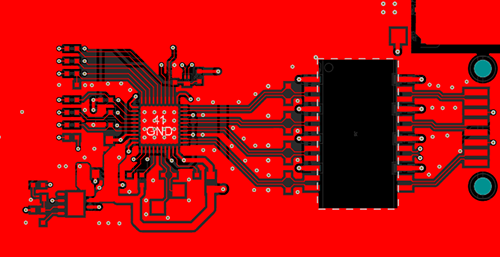

AKU AKU AKU. Kabel tata letak chip daya

Chip daya adalah inti dari perangkat elektronik, dan memastikan integritas daya sangat penting untuk meningkatkan kinerja dan stabilitas perangkat. Kontrol integritas daya untuk chip daya terutama melibatkan penanganan rute pin daya chip dan tata letak yang benar dan kabel kapasitor decoupling. Berikut ini akan merinci pertimbangan dan saran praktis mengenai aspek -aspek ini.

A.CHIP Power Pin Routing

Perutean pin daya chip adalah bagian penting dari kontrol integritas daya. Untuk menyediakan pasokan arus yang stabil, disarankan untuk mengentalkan perutean pin listrik, umumnya dengan lebar yang sama dengan pin chip. Biasanya,Lebar minimumSeharusnya tidak kurang dari 8mil, tetapi untuk hasil yang lebih baik, cobalah untuk mencapai lebar 10mil. Dengan meningkatkan lebar perutean, impedansi dapat dikurangi, sehingga mengurangi kebisingan daya dan memastikan pasokan arus yang cukup ke chip.

B. Layout dan perutean kapasitor decoupling

Kapasitor decoupling memainkan peran penting dalam kontrol integritas daya untuk chip daya. Bergantung pada karakteristik kapasitor dan persyaratan aplikasi, kapasitor decoupling umumnya dibagi menjadi kapasitor besar dan kecil.

A. Kapasitor besar: Kapasitor besar biasanya didistribusikan secara merata di sekitar chip. Karena frekuensi resonansi yang lebih rendah dan jari-jari penyaringan yang lebih besar, mereka dapat secara efektif menyaring kebisingan frekuensi rendah dan menyediakan catu daya yang stabil.

B. Kapasitor kecil: Kapasitor kecil memiliki frekuensi resonansi yang lebih tinggi dan jari -jari penyaringan yang lebih kecil, sehingga harus ditempatkan sedekat mungkin dengan pin chip. Menempatkan mereka terlalu jauh mungkin tidak secara efektif menyaring kebisingan frekuensi tinggi, kehilangan efek decoupling. Tata letak yang benar memastikan bahwa efektivitas kapasitor kecil dalam menyaring kebisingan frekuensi tinggi sepenuhnya digunakan.

C. Metode Berwatifan Kapasitor Decoupling Paralel

Untuk lebih meningkatkan integritas daya, beberapa kapasitor decoupling sering terhubung secara paralel. Tujuan utama dari praktik ini adalah untuk mengurangi induktansi seri setara (ESL) dari kapasitor individu melalui koneksi paralel.

Saat sejajar dengan beberapa kapasitor decoupling, perhatian harus diberikan pada penempatan vias untuk kapasitor. Praktik umum adalah mengimbangi vias kekuatan dan darat. Tujuan utama dari ini adalah untuk mengurangi induktansi timbal balik antara kapasitor decoupling. Pastikan bahwa induktansi timbal balik jauh lebih kecil dari ESL dari kapasitor tunggal, sehingga impedansi ESL secara keseluruhan setelah paralel dengan beberapa kapasitor decoupling adalah 1/N. Dengan mengurangi induktansi timbal balik, efisiensi penyaringan dapat ditingkatkan secara efektif, memastikan peningkatan stabilitas daya.

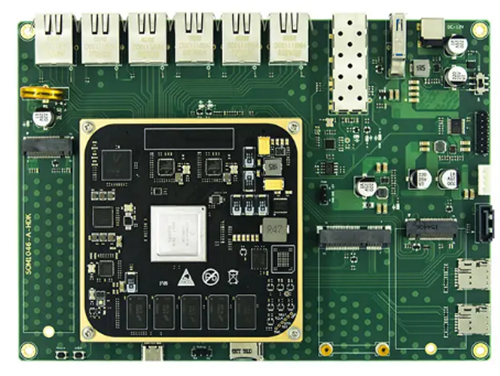

Tata letakdan perutean modul daya, perencanaan desain bidang lapisan dalam, dan penanganan tata letak dan kabel power chip yang benar sangat diperlukan dalam desain perangkat elektronik. Melalui tata letak dan perutean yang tepat, kami dapat memastikan stabilitas dan efisiensi modul daya, mengurangi gangguan kebisingan, dan meningkatkan kinerja keseluruhan. Desain tumpukan layer dan segmentasi daya berganda lebih lanjut mengoptimalkan karakteristik bidang daya, mengurangi gangguan kebisingan daya. Penanganan tata letak dan kabel dan kapasitor decoupling chip yang tepat sangat penting untuk kontrol integritas daya, memastikan pasokan arus yang stabil dan pemfilteran kebisingan yang efektif, meningkatkan kinerja dan stabilitas perangkat.

Dalam pekerjaan praktis, berbagai faktor seperti besarnya saat ini, lebar perutean, jumlah vias, efek kopling, dll., Perlu secara komprehensif dipertimbangkan untuk membuat keputusan tata letak dan perutean yang rasional. Ikuti spesifikasi desain dan praktik terbaik untuk memastikan kontrol dan optimalisasi integritas daya. Hanya dengan cara ini kita dapat menyediakan catu daya yang stabil dan efisien untuk perangkat elektronik, memenuhi permintaan kinerja yang meningkat, dan mendorong pengembangan dan kemajuan teknologi elektronik.

Shenzhen Anke PCB Co., Ltd

Waktu posting: Mar-25-2024